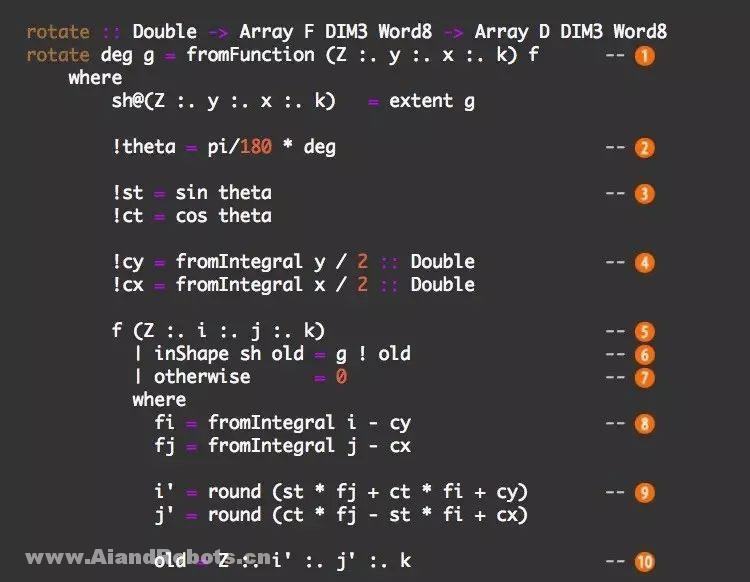

5 时序逻辑

VL33 非整数倍数据位宽转换8to12

和上一题一样的,注意valid_out输出时加一个valid_in(其实32题也要加,不过不加仿真也能过)。

`timescale 1ns/1ns

module width_8to12(

input clk ,

input rst_n ,

input valid_in ,

input [7:0] data_in ,

output reg valid_out,

output reg [11:0] data_out

);

reg [2:0]count;

always@(posedge clk or negedge rst_n)

begin

if(~rst_n)

count <= 0;

else if(valid_in)

count <= (count<2)?count + 1:0;

end

always@(posedge clk or negedge rst_n)

begin

if(~rst_n)

valid_out <= 0;

else if(valid_in&&(count==1||count==2))

valid_out <= 1;

else

valid_out <= 0;

end

reg [11:0]data_lock;

always@(posedge clk or negedge rst_n)

begin

if(~rst_n)begin

data_lock <= 0;

data_out <= 0;

end else if(valid_in)begin

data_lock <= {data_lock[3:0],data_in};

if(count == 1)

data_out <= {data_lock[7:0],data_in[7:4]};

else if(count == 2)

data_out <= {data_lock[3:0],data_in};

end

end

endmodule